От песка до процессора. AMD Llano: последние соки Атлона

Производство микросхем — весьма непростое дело, и закрытость этого рынка диктуется в первую очередь особенностями главенствующей в наши дни технологии фотолитографии. Микроскопические электронные схемы проецируются на кремниевую пластину через фотошаблоны, стоимость каждого из которых может достигать $200 000. А между тем для изготовления одного чипа требуется не меньше 50 таких масок. Добавьте к этому стоимость «проб и ошибок» при разработке новых моделей, и вы поймете, что производить процессоры могут только очень большие компании очень большими тиражами.

А что делать научным лабораториям и высокотехнологичным стартапам, которым необходимы нестандартные схемы? Как быть военным, для которых закупать процессоры у «вероятного противника» — мягко говоря, не комильфо?

Мы побывали на российском производственном участке голландской компании Mapper, благодаря которой изготовление микросхем может перестать быть уделом небожителей и превратится в занятие для простых смертных. Ну или почти простых. Здесь, на территории Технополиса «Москва» при финансовой поддержке корпорации «Роснано» производится ключевой компонент технологии Mapper — электронно-оптическая система.

Однако прежде чем разбираться в нюансах безмасочной литографии Mapper, стоит вспомнить основы обычной фотолитографии.

Неповоротливый свет

На современном процессоре Intel Core i7 может располагаться около 2 млрд транзисторов (в зависимости от модели), размер каждого из которых — 14 нм. В погоне за вычислительной мощностью производители ежегодно уменьшают размеры транзисторов и увеличивают их число. Вероятным технологическим пределом в этой гонке можно считать 5 нм: на таких расстояниях начинают проявляться квантовые эффекты, из-за которых электроны в соседних ячейках могут вести себя непредсказуемо.

Чтобы нанести на кремниевую пластину микроскопические полупроводниковые структуры, используют процесс, похожий на работу с фотоувеличителем. Разве что цель у него обратная — сделать изображение как можно меньше. Пластину (или защитную пленку) покрывают фоторезистом — полимерным фоточувствительным материалом, который меняет свои свойства при облучении светом. Требуемый рисунок чипа экспонируют на фоторезист через маску и собирающую линзу. Напечатанные пластины, как правило, в четыре раза меньше, чем маски.

Такие вещества, как кремний или германий, имеют по четыре электрона на внешнем энергетическом уровне. Они образуют красивые кристаллы, похожие на металл. Но, в отличие от металла, они не проводят электрический ток: все их электроны задействованы в мощных ковалентных связях и не могут двигаться. Однако все меняется, если добавить к ним немного донорной примеси из вещества с пятью электронами на внешнем уровне (фосфора или мышьяка). Четыре электрона вступают в связь с кремнием, а один остается свободным. Кремний с донорной примесью (n-типа) — неплохой проводник. Если добавить к кремнию акцепторную примесь из вещества с тремя электронами на внешнем уровне (бор, индий), аналогичным образом образуются «дырки», виртуальный аналог положительного заряда. В таком случае речь идет о полупроводнике p-типа.

Соединив проводники p- и n-типа, мы получим диод — полупроводниковый прибор, пропускающий ток только в одном направлении. Комбинация p-n-p или n-p-n дает нам транзистор — через него ток протекает только в том случае, если на центральный проводник подается определенное напряжение.

Такие вещества, как кремний или германий, имеют по четыре электрона на внешнем энергетическом уровне. Они образуют красивые кристаллы, похожие на металл. Но, в отличие от металла, они не проводят электрический ток: все их электроны задействованы в мощных ковалентных связях и не могут двигаться. Однако все меняется, если добавить к ним немного донорной примеси из вещества с пятью электронами на внешнем уровне (фосфора или мышьяка). Четыре электрона вступают в связь с кремнием, а один остается свободным. Кремний с донорной примесью (n-типа) — неплохой проводник. Если добавить к кремнию акцепторную примесь из вещества с тремя электронами на внешнем уровне (бор, индий), аналогичным образом образуются «дырки», виртуальный аналог положительного заряда. В таком случае речь идет о полупроводнике p-типа.

Соединив проводники p- и n-типа, мы получим диод — полупроводниковый прибор, пропускающий ток только в одном направлении. Комбинация p-n-p или n-p-n дает нам транзистор — через него ток протекает только в том случае, если на центральный проводник подается определенное напряжение.

Свои коррективы в этот процесс вносит дифракция света: луч, проходя через отверстия маски, немного преломляется, и вместо одной точки экспонируется серия концентрических кругов, как от брошенного в омут камня. К счастью, дифракция находится в обратной зависимости от длины волны, чем и пользуются инженеры, применяя свет ультрафиолетового диапазона с длиной волны 195 нм. Почему не еще меньше? Просто более короткая волна не будет преломляться собирающей линзой, лучи будут проходить насквозь, не фокусируясь. Увеличить собирающую способность линзы тоже нельзя — не позволит сферическая аберрация: каждый луч будет проходить оптическую ось в своей точке, нарушая фокусировку.

Максимальная ширина контура, которую можно отобразить с помощью фотолитографии, — 70 нм. Чипы с более высоким разрешением печатают в несколько приемов: наносят 70-нанометровые контуры, протравливают схему, а затем экспонируют следующую часть через новую маску.

Сейчас в разработке находится технология фотолитографии в глубоком ультрафиолете, с применением света с экстремальной длиной волны около 13,5 нм. Технология предполагает использование вакуума и многослойных зеркал с отражением на основе межслойной интерференции. Маска тоже будет не просвечивающим, а отражающим элементом. Зеркала лишены явления преломления, поэтому могут работать со светом любой длины волны. Но пока это лишь концепция, которую, возможно, станут применять в будущем.

Как сегодня делают процессоры

Идеально отполированную круглую кремниевую пластину диаметром 30 см покрывают тонким слоем фоторезиста. Равномерно распределить фоторезист помогает центробежная сила.

Будущая схема экспонируется на фоторезист через маску. Этот процесс повторяется многократно, потому что из одной пластины получается множество чипов.

Та часть фоторезиста, которая подверглась ультрафиолетовому излучению, становится растворимой и с легкостью удаляется с помощью химикатов.

Участки кремниевой пластины, не защищенные фоторезистом, подвергаются химическому травлению. На их месте образуются углубления.

На пластину вновь наносят слой фоторезиста. На этот раз с помощью экспонирования обнажают те участки, которые подвергнутся ионной бомбардировке.

Под воздействием электрического поля ионы примесей разгоняются до скоростей более 300 000 км/ч и проникают в кремний, придавая ему свойства полупроводника.

После удаления остатков фоторезиста на пластине остаются готовые транзисторы. Сверху наносят слой диэлектрика, в котором по все той же технологии протравливают отверстия под контакты.

Пластину помещают в раствор сульфата меди, и с помощью электролиза на нее наносят проводящий слой. Затем весь слой снимают шлифовкой, а контакты в отверстиях остаются.

Контакты соединяются многоэтажной сетью из металлических «проводов». Количество «этажей» может достигать 20, а общая схема проводников называется архитектурой процессора.

Только теперь пластину распиливают на множество отдельных чипов. Каждый «кристалл» тестируют и лишь затем устанавливают на плату с контактами и накрывают серебряной крышкой-радиатором.

13 000 телевизоров

Альтернативой фотолитографии считают электролитографию, когда экспонируют не светом, а электронами, и не фото-, а электрорезист. Электронный пучок легко фокусируется в точку минимального размера, вплоть до 1 нм. Технология напоминает электронно-лучевую трубку телевизора: сфокусированный поток электронов отклоняется управляющими катушками, рисуя изображение на кремниевой пластине.

До последнего времени эта технология не могла конкурировать с традиционным методом из-за низкой скорости. Чтобы электрорезист среагировал на облучение, он должен принять определенное количество электронов на единицу площади, поэтому один луч может экспонировать в лучшем случае 1 см2/ч. Это приемлемо для единичных заказов от лабораторий, однако неприменимо в промышленности.

К сожалению, решить проблему, увеличив энергию луча, невозможно: одноименные заряды отталкиваются, поэтому при увеличении тока пучок электронов становится шире. Зато можно увеличить количество лучей, экспонируя несколько зон одновременно. И если несколько — это 13 000, как в технологии Mapper, то, согласно расчетам, можно печатать уже десять полноценных чипов в час.

Конечно, объединить в одном устройстве 13 000 электронно-лучевых трубок было бы невозможно. В случае Mapper излучение из источника направляется на коллиматорную линзу, которая формирует широкий параллельный пучок электронов. На его пути встает апертурная матрица, которая превращает его в 13 000 отдельных лучей. Лучи проходят через матрицу бланкеров — кремниевую пластину с 13 000 отверстий. Около каждого из них располагается отклоняющий электрод. Если на него подается ток, электроны «промахиваются» мимо своего отверстия, и один из 13 000 лучей выключается.

Пройдя бланкеры, лучи направляются к матрице дефлекторов, каждый из которых может отклонять свой луч на пару микронов вправо или влево относительно движения пластины (так что Mapper все же напоминает 13 000 кинескопов). Наконец, каждый луч дополнительно фокусируется собственной микролинзой, после чего направляется к электрорезисту. На сегодняшний день технология Mapper прошла тестирование во французском научно-исследовательском институте микроэлектроники CEA-Leti и в компании TSMC, которая производит микропроцессоры для ведущих игроков рынка (в том числе и для Apple iPhone 6S). Ключевые компоненты системы, включая кремниевые электронные линзы, производятся на московском заводе.

Технология Mapper обещает новые перспективы не только исследовательским лабораториям и мелкосерийным (в том числе военным) производствам, но и крупным игрокам. В настоящее время для тестирования прототипов новых процессоров приходится изготавливать точно такие же фотошаблоны, как для массового производства. Возможность относительно быстрого прототипирования схем обещает не только снизить стоимость разработки, но и ускорить прогресс в этой области. Что в конечном счете на руку массовому потребителю электроники, то есть всем нам.

Корни нашего цифрового образа жизни определённо растут из полупроводников, которые позволили создавать сложные вычислительные чипы на основе транзисторов. Они хранят и обрабатывают данные, что и является основой современных микропроцессоров. Полупроводники, которые сегодня изготавливаются из песка, являются ключевым компонентом практически любого электронного устройства, от компьютеров до ноутбуков и сотовых телефонов. Даже машины теперь не обходятся без полупроводников и электроники, поскольку полупроводники управляют системой кондиционирования воздуха, процессом впрыска топлива, зажиганием, люком, зеркалами и даже рулевым управлением (BMW Active Steering). Сегодня почти любое устройство, которое потребляет энергию, построено на полупроводниках.

Микропроцессоры, без сомнения, находятся среди самых сложных полупроводниковых продуктов, поскольку в скором времени число транзисторов достигнет миллиарда, а спектр функциональности поражает уже сегодня. Скоро выйдут двуядерные процессоры Core 2 на почти готовом 45-нм техпроцессе Intel, причём содержать они будут уже 410 миллионов транзисторов (хотя их большая часть будет использоваться для 6-Мбайт кэша L2). 45-нм процесс назван так по размеру одного транзистора, который теперь примерно в 1 000 раз меньше диаметра человеческого волоса. В определённой степени именно поэтому электроника начинает управлять всем в нашей жизни: даже когда размеры транзистора были больше, производить не очень сложные микросхемы было очень дёшево, бюджет транзисторов был весьма большим.

В нашей статье мы рассмотрим основы производства микропроцессоров, но также коснёмся и истории процессоров, архитектуры и рассмотрим разные продукты на рынке. В Интернете можно найти немало интересной информации, кое-что перечислено ниже.

- Wikipedia: Microprocessor . В этой статье рассмотрены разные типы процессоров и приведены ссылки на производителей и дополнительные страницы Wiki, посвящённые процессорам.

- Wikipedia: Microprocessors (Category) . В разделе, посвящённом микропроцессорам, приведено ещё больше ссылок и информации.

Конкуренты в сфере ПК: AMD и Intel

Штаб-квартира компании Advanced Micro Devices Inc., основанной в 1969, располагается в калифорнийском Саннивейле, а "сердце" компании Intel, которая была образована всего на год раньше, располагается в нескольких километрах, в городе Санта-Клара. У AMD сегодня есть два завода: в Остине (Техас, США) и в Дрездене (Германия). Скоро в действие вступит новый завод. Кроме того, AMD объединила усилия с IBM по разработке процессорных технологий и по производству. Конечно, всё это - лишь доля от размера Intel, поскольку у этого лидера рынка сегодня работают почти 20 заводов в девяти местах. Примерно половина из них используется для производства микропроцессоров. Поэтому, когда вы сравниваете AMD и Intel, помните, что вы сравниваете Давида и Голиафа.

У Intel есть бесспорное преимущество в виде огромных производственных мощностей. Да, компания сегодня лидирует по внедрению передовых технологических процессов. Intel примерно на год опережает AMD в этом отношении. В результате Intel может использовать в своих процессорах большее число транзисторов и больший объём кэша. AMD, в отличие от Intel, приходится максимально эффективно оптимизировать техпроцесс, чтобы не отстать от конкурента и выпускать достойные процессоры. Конечно, дизайн процессоров и их архитектура сильно различаются, но технический процесс производства построен на тех же базовых принципах. Хотя, конечно, и в нём отличий много.

Производство микропроцессоров

Производство микропроцессоров состоит из двух важных этапов. Первый заключается в производстве подложки, что AMD и Intel осуществляют на своих заводах. Сюда входит и придание подложке проводящих свойств. Второй этап - тест подложек, сборка и упаковка процессора. Последнюю операцию обычно производят в менее дорогих странах. Если вы посмотрите на процессоры Intel, то найдёте надпись, что упаковка была осуществлена в Коста-Рике, Малайзии, на Филиппинах и т.д.

AMD и Intel сегодня пытаются выпускать продукты для максимального числа сегментов рынка, причём, на основе минимально возможного ассортимента кристаллов. Прекрасный пример - линейка процессоров Intel Core 2 Duo. Здесь есть три процессора с кодовыми названиями для разных рынков: Merom для мобильных приложений, Conroe - настольная версия, Woodcrest - серверная версия. Все три процессора построены на одной технологической основе, что позволяет производителю принимать решения на последних этапах производства. Можно включать или отключать функции, а текущий уровень тактовых частот даёт Intel прекрасный процент выхода годных кристаллов. Если на рынке повысился спрос на мобильные процессоры, Intel может сфокусироваться на выпуске моделей Socket 479. Если возрос спрос на настольные модели, то компания будет тестировать, валидировать и упаковывать кристаллы для Socket 775, в то время как серверные процессоры упаковываются под Socket 771. Так создаются даже четырёхядерные процессоры: два двуядерных кристалла устанавливаются в одну упаковку, вот мы и получаем четыре ядра.

Как создаются чипы

Производство чипов заключается в наложении тонких слоёв со сложным "узором" на кремниевые подложки. Сначала создаётся изолирующий слой, который работает как электрический затвор. Сверху затем накладывается фоторезистивный материал, а нежелательные участки удаляются с помощью масок и высокоинтенсивного облучения. Когда облучённые участки будут удалены, под ними откроются участки диоксида кремния, который удаляется с помощью травления. После этого удаляется и фоторезистивный материал, и мы получаем определённую структуру на поверхности кремния. Затем проводятся дополнительные процессы фотолитографии, с разными материалами, пока не будет получена желаемая трёхмерная структура. Каждый слой можно легировать определённым веществом или ионами, меняя электрические свойства. В каждом слое создаются окна, чтобы затем подводить металлические соединения.

Что касается производства подложек, то из цельного монокристалла-цилиндра их необходимо нарезать тонкими "блинами", чтобы потом легко разрезать на отдельные кристаллы процессоров. На каждом шаге производства выполняется сложное тестирование, позволяющее оценить качество. Для тестов каждого кристалла на подложке используются электрические зонды. Наконец, подложка разрезается на отдельные ядра, нерабочие ядра сразу же отсеиваются. В зависимости от характеристик, ядро становится тем или иным процессором и заключается в упаковку, которая облегчает установку процессора на материнскую плату. Все функциональные блоки проходят через интенсивные стресс-тесты.

Всё начинается с подложек

Первый шаг в производстве процессоров выполняется в чистой комнате. Кстати, важно отметить, что подобное технологичное производство представляет собой скопление огромного капитала на квадратный метр. На постройку современного завода со всем оборудованием легко "улетают" 2-3 млрд. долларов, да и на тестовые прогоны новых технологий требуется несколько месяцев. Только затем завод может серийно выпускать процессоры.

В общем, процесс производства чипов состоит из нескольких шагов обработки подложек. Сюда входит и создание самих подложек, которые в итоге будут разрезаны на отдельные кристаллы.

Всё начинается с выращивания монокристалла, для чего затравочный кристалл внедряется в ванну с расплавленным кремнием, который находится чуть выше точки плавления поликристаллического кремния. Важно, чтобы кристаллы росли медленно (примерно день), чтобы гарантировать правильное расположение атомов. Поликристаллический или аморфный кремний состоит из множества разномастных кристаллов, которые приведут к появлению нежелательных поверхностных структур с плохими электрическими свойствами. Когда кремний будет расплавлен, его можно легировать с помощью других веществ, меняющих его электрические свойства. Весь процесс происходит в герметичном помещении со специальным воздушным составом, чтобы кремний не окислялся.

Монокристалл разрезается на "блины" с помощью кольцевой алмазной пилы, которая очень точная и не создаёт крупных неровностей на поверхности подложек. Конечно, при этом поверхность подложек всё равно не идеально плоская, поэтому нужны дополнительные операции.

Сначала с помощью вращающихся стальных пластин и абразивного материала (такого, как оксид алюминия), снимается толстый слой с подложек (процесс называется притиркой). В результате устраняются неровности размером от 0,05 мм до, примерно, 0,002 мм (2 000 нм). Затем следует закруглить края каждой подложки, поскольку при острых кромках могут отслаиваться слои. Далее используется процесс травления, когда с помощью разных химикатов (плавиковая кислота, уксусная кислота, азотная кислота) поверхность сглаживается ещё примерно на 50 мкм. Физически поверхность не ухудшается, поскольку весь процесс полностью химический. Он позволяет удалить оставшиеся погрешности в структуре кристалла, в результате чего поверхность будет близка к идеалу.

Последний шаг - полировка, которая сглаживает поверхность до неровностей, максимум, 3 нм. Полировка осуществляется с помощью смеси гидроксида натрия и гранулированного диоксида кремния.

Сегодня подложки для микропроцессоров имеют диаметр 200 или 300 мм, что позволяет производителям чипов получать с каждой из них множество процессоров. Следующим шагом будут 450-мм подложки, но раньше 2013 года ожидать их не следует. В целом, чем больше диаметр подложки, тем больше можно произвести чипов одинакового размера. 300-мм подложка, например, даёт более чем в два раза больше процессоров, чем 200-мм.

Мы уже упоминали легирование, которое выполняется во время роста монокристалла. Но легирование производится и с готовой подложкой, и во время процессов фотолитографии позднее. Это позволяет менять электрические свойства определённых областей и слоёв, а не всей структуры кристалла

Добавление легирующего вещества может происходить через диффузию. Атомы легирующего вещества заполняют свободное пространство внутри кристаллической решётки, между структурами кремния. В некоторых случаях можно легировать и существующую структуру. Диффузия осуществляется с помощью газов (азот и аргон) или с помощью твёрдых веществ или других источников легирующего вещества.

Ещё один подход к легированию заключается в ионной имплантации, которая очень полезна в деле изменения свойств подложки, которая была легирована, поскольку ионная имплантация осуществляется при обычной температуре. Поэтому существующие примеси не диффундируют. На подложку можно наложить маску, которая позволяет обрабатывать только определённые области. Конечно, об ионной имплантации можно говорить долго и обсуждать глубину проникновения, активацию добавки при высокой температуре, канальные эффекты, проникновение в оксидные уровни и т.д., но это выходит за рамки нашей статьи. Процедуру можно повторять несколько раз во время производства.

Чтобы создать участки интегральной схемы, используется процесс фотолитографии. Поскольку при этом нужно облучать не всю поверхность подложки, то важно использовать так называемые маски, которые пропускают излучение высокой интенсивности только на определённые участки. Маски можно сравнить с чёрно-белым негативом. Интегральные схемы имеют множество слоёв (20 и больше), и для каждого из них требуется своя маска.

Структура из тонкой хромовой плёнки наносится на поверхность пластины из кварцевого стекла, чтобы создать шаблон. При этом дорогие инструменты, использующие поток электронов или лазер, прописывают необходимые данные интегральной схемы, в результате чего мы получаем шаблон из хрома на поверхности кварцевой подложки. Важно понимать, что каждая модификация интегральной схемы приводит к необходимости производства новых масок, поэтому весь процесс внесения правок очень затратный. Для очень сложных схем маски создаются весьма долго.

С помощью фотолитографии на кремниевой подложке формируется структура. Процесс повторяется несколько раз, пока не будет создано множество слоёв (более 20). Слои могут состоять из разных материалов, причём, нужно ещё и продумывать соединения микроскопическими проволочками. Все слои можно легировать.

Перед тем, как начнётся процесс фотолитографии, подложка очищается и нагревается, чтобы удалить липкие частицы и воду. Затем подложка с помощью специального устройства покрывается диоксидом кремния. Далее на подложку наносится связывающий агент, который гарантирует, что фоторезистивный материал, который будет нанесён на следующем шаге, останется на подложке. Фоторезистивный материал наносится на середину подложки, которая потом начинает вращаться с большой скоростью, чтобы слой равномерно распределился по всей поверхности подложки. Подложка вновь затем нагревается.

Затем через маску обложка облучается квантовым лазером, жёстким ультрафиолетовым излучением, рентгеновским излучением, пучками электронов или ионов - могут использоваться все эти источники света или энергии. Пучки электронов применяются, главным образом, для создания масок, рентгеновские лучи и пучки ионов - для исследовательских целей, а в промышленном производстве сегодня доминируют жёсткое УФ-излучение и газовые лазеры.

Жёсткое УФ-излучение с длиной волны 13,5 нм облучает фоторезистивный материал, проходя через маску.

Для получения требуемого результата очень важны время проецирования и фокусировка. Плохая фокусировка приведёт к тому, что останутся лишние частицы фоторезистивного материала, поскольку некоторые отверстия в маске не будут облучены должным образом. То же самое получится, если время проецирования будет слишком маленьким. Тогда структура из фоторезистивного материала будет слишком широкой, участки под отверстиями будут недодержанными. С другой стороны, чрезмерное время проецирования создаёт слишком большие участки под отверстиями и слишком узкую структуру из фоторезистивного материала. Как правило, очень трудоёмко и сложно отрегулировать и оптимизировать процесс. Неудачная регулировка приведёт к серьёзным отклонениям и в соединительных проводниках.

Специальная шаговая проекционная установка перемещает подложку в нужное положение. Затем может проецироваться строчка или один участок, чаще всего соответствующий одному кристаллу процессора. Дополнительные микроустановки могут вносить дополнительные изменения. Они могут отлаживать существующую технологию и оптимизировать техпроцесс. Микроустановки обычно работают над площадями меньше 1 кв. мм, в то время как обычные установки покрывают площади большего размера.

Затем подложка переходит на новый этап, где удаляется ослабленный фоторезистивный материал, что позволяет получить доступ к диоксиду кремния. Существуют мокрый и сухой процессы травления, которыми обрабатываются участки диоксида кремния. Мокрые процессы используют химические соединения, а сухие процессы - газ. Отдельный процесс заключается и в удалении остатков фоторезистивного материала. Производители часто сочетают мокрое и сухое удаление, чтобы фоторезистивный материал был полностью удалён. Это важно, поскольку фоторезистивный материал органический, и если его не удалить, он может привести к появлению дефектов на подложке. После травления и очистки можно приступать к осмотру подложки, что обычно и происходит на каждом важном этапе, или переводить подложку на новый цикл фотолитографии.

Тест подложек, сборка, упаковка

Готовые подложки тестируются на так называемых установках зондового контроля. Они работают со всей подложкой. На контакты каждого кристалла накладываются контакты зонда, что позволяет проводить электрические тесты. С помощью программного обеспечения тестируются все функции каждого ядра.

С помощью разрезания из подложки можно получить отдельные ядра. На данный момент установки зондового контроля уже выявили, какие кристаллы содержат ошибки, поэтому после разрезания их можно отделить от годных. Раньше повреждённые кристаллы физически маркировались, теперь в этом нет необходимости, вся информация хранится в единой базе данных.

Крепление кристалла

Затем функциональное ядро нужно связать с процессорной упаковкой, используя клейкий материал.

Затем нужно провести проводные соединения, связывающие контакты или ножки упаковки и сам кристалл. Могут использоваться золотые, алюминиевые или медные соединения.

Большинство современных процессоров используют пластиковую упаковку с распределителем тепла.

Обычно ядро заключается в керамическую или пластиковую упаковку, что позволяет предотвратить повреждение. Современные процессоры оснащаются так называемым распределителем тепла, который обеспечивает дополнительную защиту кристалла, а также большую контактную поверхность с кулером.

Тестирование процессора

Последний этап подразумевает тестирование процессора, что происходит при повышенных температурах, в соответствии со спецификациями процессора. Процессор автоматически устанавливается в тестовый сокет, после чего происходит анализ всех необходимых функций.

Современные микропроцессоры - одни из сложнейших устройств, изготавливаемых человеком. Производство полупроводникового кристалла намного более ресурсоемко, чем, скажем, возведение многоэтажного дома или организация крупнейшего выставочного мероприятия. Однако благодаря массовому выпуску CPU в денежном эквиваленте мы этого не замечаем, да и редко кто задумывается обо всей грандиозности элементов, занимающих столь видное место внутри системного блока. Мы решили изучить детали производства процессоров и поведать о них в данном материале. Благо в Сети сегодня достаточно информации на эту тему, а специализированная подборка презентаций и слайдов корпорации Intel позволяет выполнить поставленную задачу максимально наглядно. Предприятия других гигантов полупроводниковой индустрии работают по тому же принципу, поэтому с уверенностью можно сказать, что все современные микросхемы проходят идентичный путь создания.

|

|

|

|

|

|

|

|

Первое, о чем стоит упомянуть, - строительный материал для процессоров. Кремний (англ. silicon) - второй после кислорода наиболее распространенный элемент на планете. Он является природным полупроводником и используется как основной материал для производства чипов всевозможных микросхем. Больше всего кремния содержится в обычном песке (особенно кварце) в виде диоксида кремния (SiO2).

Впрочем, кремний - не единственный материал. Самый близкий его родственник и заменитель - германий, однако в процессе совершенствования производства ученые выявляют хорошие полупроводниковые свойства у соединений других элементов и готовятся опробовать их на практике или уже это делают.

1 Кремний проходит многоступенчатый процесс очистки: сырье для микросхем не может содержать больше примесей, чем один чужеродный атом на миллиард.

2 Кремний расплавляют в специальной емкости и, опустив внутрь постоянно охлаждаемый вращающийся стержень, «наматывают» на него благодаря силам поверхностного натяжения вещество.

3 В итоге получаются продольные заготовки (монокристаллы) круглого сечения, каждая массой около 100 кг.

4 Заготовку нарезают на отдельные кремниевые диски - пластины, на которых будут расположены сотни микропроцессоров. Для этих целей используются станки с алмазными режущими дисками или проволочно-абразивные установки.

5 Подложки полируют до зеркального блеска, чтобы устранить все дефекты на поверхности. Следующий шаг - нанесение тончайшего фотополимерного слоя.

6 Обработанная подложка подвергается воздействию жесткого ультрафиолетового излучения. В фотополимерном слое происходит химическая реакция: свет, проходя через многочисленные трафареты, повторяет рисунки слоев CPU.

7 Реальный размер наносимого изображения в несколько раз меньше собственно трафарета.

8 Участки, «протравленные» излучением, вымываются. На кремниевой подложке получается рисунок, который затем подвергается закреплению.

9 Следующий этап изготовления одного слоя - ионизация, в процессе которой свободные от полимера участки кремния бомбардируются ионами.

10 В местах их попадания изменяются свойства электрической проводимости.

11 Оставшийся полимер удаляют, и транзистор почти готов. В изолирующих слоях делаются отверстия, которые благодаря химической реакции заполняются атомами меди, используемыми в качестве контактов.

12 Соединение транзисторов представляет собой многоуровневую разводку. Если взглянуть в микроскоп, на кристалле можно заметить множество металлических проводников и помещенных между ними атомов кремния или его современных заменителей.

13 Часть готовой подложки проходит первый тест на функциональность. На этом этапе на каждый из выбранных транзисторов подается ток, и автоматизированная система проверяет параметры работы полупроводника.

14 Подложка с помощью тончайших режущих кругов разрезается на отдельные части.

15 Годные кристаллы, полученные в результате данной операции, используются в производстве процессоров, а бракованные отправляются в отходы.

16 Отдельный кристалл, из которого будет сделан процессор, помещают между основанием (подложкой) CPU и теплорас-пределительной крышкой и «упаковывают».

17 В ходе окончательного тестирования готовые процессоры проверяются на соответствие требуемым параметрам и лишь затем сортируются. На основании полученных данных в них прошивается микрокод, позволяющий системе должным образом определить CPU.

18 Готовые устройства упаковываются и направляются на рынок.

|

|

|

|

Интересные факты о процессорах и их производстве

«Силиконовая долина» (Silicon Valley, США, Калифорния)

Получила свое название благодаря основному строительному элементу, использующемуся в производстве микрочипов.

«Почему пластины для производства процессоров круглые?» - наверняка спросите вы.

Для производства кремниевых кристаллов применяется технология, позволяющая получать только цилиндрические заготовки, которые затем режутся на части. До сих пор еще никому не удавалось изготовить квадратную пластину, лишенную дефектов.

Почему микрочипы квадратные?

Именно такая литография позволяет использовать площадь пластины с максимальной эффективностью.

Зачем процессорам столько ножек/контактов?

Помимо сигнальных линий каждый процессор для работы нуждается в стабильном питании. При энергопотреблении порядка 100-120 Вт и низком напряжении через контакты может протекать ток силой до 100 А. Значительная часть контактов CPU выделена именно под систему питания и дублируется.

Утилизация отходов производства

Раньше дефектные пластины, их остатки и бракованные микрочипы шли в отходы. На сегодняшний день ведутся разработки, позволяющие использовать их в качестве основы для производства солнечных батарей.

«Костюм кролика».

Такое название получил комбинезон белого цвета, который обязаны носить все рабочие производственных помещений. Делается это для поддержания максимальной чистоты и защиты от случайного попадания частиц пыли на производственные установки. «Костюм кролика» впервые был использован на фабриках по производству процессоров в 1973 году и с тех пор стал общепринятым стандартом.

99,9999%

Для производства процессоров пригоден только кремний высочайшей степени чистоты. Заготовки очищают спецхимией.

300 мм

Таков диаметр современных кремниевых пластин для производства процессоров.

1000 раз

Именно настолько чище воздух в помещениях фабрик для производства чипов, чем в операционной.

20 слоев

Процессорный кристалл очень тонкий (меньше миллиметра), но в нем умещаются более 20 слоев сложнейших структурных объединений транзисторов, которые выглядят как многоуровневые хайвеи.

2500

Именно столько кристаллов процессора Intel Atom (имеют наименьшую площадь среди cовременных CPU) размещаются на одной 300-миллиметровой пластине.

10 000 000 000 000 000 000

Сто квинтиллионов транзисторов в виде структурных элементов микрочипов отгружаются с фабрик каждый год. Это приблизительно в 100 раз больше, чем оценочное количество муравьев на планете.

A

Стоимость производства одного транзистора в процессоре сегодня равна цене печати одной буквы в газете.

В процессе подготовки статьи использовались материалы с официального веб-сайта корпорации Intel, www.intel.ua

Практически все знают, что в компьютере главным элементом среди всех «железных» компонентов является центральный процессор. Но круг людей, которые представляют себе, как работает процессор, является весьма ограниченным. Большинство пользователей об этом и понятия не имеют. И даже когда система вдруг начинает «тормозить», многие считают, что это процессор плохо работает, и не придают значения другим факторам. Для полного понимания ситуации рассмотрим некоторые аспекты работы ЦП.

Что такое центральный процессор?

Из чего состоит процессор?

Если говорить о том, как работает процессор Intel или его конкурент AMD, нужно посмотреть, как устроены эти чипы. Первый микропроцессор (кстати, именно от Intel, модель 4040) появился еще в далеком 1971 году. Он мог выполнять только простейшие операции сложения и вычитания с обработкой всего лишь 4 бит информации, т. е. имел 4-битную архитектуру.

Современные процессоры, как и первенец, основаны на транзисторах и обладают куда большим быстродействием. Изготавливаются они методом фотолитографии из определенного числа отдельных кремниевых пластинок, составляющих единый кристалл, в который как бы впечатаны транзисторы. Схема создается на специальном ускорителе разогнанными ионами бора. Во внутренней структуре процессоров основными компонентами являются ядра, шины и функциональные частицы, называемые ревизиями.

Основные характеристики

Как и любое другое устройство, процессор характеризуется определенными параметрами, которые, отвечая на вопрос, как работает процессор, обойти стороной нельзя. Прежде всего это:

- количество ядер;

- число потоков;

- размер кэша (внутренней памяти);

- тактовая частота;

- быстрота шины.

Пока остановимся на тактовой частоте. Не зря процессор называют сердцем компьютера. Как и сердце, он работает в режиме пульсации с определенным количеством тактов в секунду. Тактовая частота измеряется в МГц или в ГГц. Чем она выше, тем больше операций может выполнить устройство.

На какой частоте работает процессор, можно узнать из его заявленных характеристик или посмотреть информацию в Но в процессе обработки команд частота может меняться, а при разгоне (оверлокинге) увеличиваться до экстремальных пределов. Таким образом, заявленная является всего лишь усредненным показателем.

Количество ядер - показатель, определяющий число вычислительных центров процессора (не путать с потоками - количество ядер и потоков могут не совпадать). За счет такого распределения появляется возможность перенаправления операций на другие ядра, за счет чего повышается общая производительность.

Как работает процессор: обработка команд

Теперь немного о структуре исполняемых команд. Если посмотреть, как работает процессор, нужно четко представлять себе, что любая команда имеет две составляющие - операционную и операндную.

Операционная часть указывает, что должна выполнить в данный момент компьютерная система, операнда определяет то, над чем должен работать именно процессор. Кроме того, ядро процессора может содержать два вычислительных центра (контейнера, потока), которые разделяют выполнение команды на несколько этапов:

- выработка;

- дешифрование;

- выполнение команды;

- обращение к памяти самого процессора

- сохранение результата.

Сегодня применяется раздельное кэширование в виде использования двух уровней кэш-памяти, что позволяет избежать перехвата двумя и более командами обращения к одному из блоков памяти.

Процессоры по типу обработки команд разделяют на линейные (выполнение команд в порядке очереди их записи), циклические и разветвляющиеся (выполнение инструкций после обработки условий ветвления).

Выполняемые операции

Среди основных функций, возложенных на процессор, в смысле выполняемых команд или инструкций различают три основные задачи:

- математические действия на основе арифметико-логического устройства;

- перемещение данных (информации) из одного типа памяти в другой;

- принятие решения по исполнению команды, и на его основе - выбор переключения на выполнения других наборов команд.

Взаимодействие с памятью (ПЗУ и ОЗУ)

В этом процессе следует отметить такие компоненты, как шина и канал чтения и записи, которые соединены с запоминающими устройствами. ПЗУ содержит постоянный набор байт. Сначала адресная шина запрашивает у ПЗУ определенный байт, затем передает его на шину данных, после чего канал чтения меняет свое состояние и ПЗУ предоставляет запрошенный байт.

Но процессоры могут не только считывать данные из оперативной памяти, но и записывать их. В этом случае используется канал записи. Но, если разобраться, по большому счету современные компьютеры чисто теоретически могли бы и вовсе обойтись без ОЗУ, поскольку современные микроконтроллеры способны размещать нужные байты данных непосредственно в памяти самого процессорного чипа. Но вот без ПЗУ обойтись никак нельзя.

Кроме всего прочего, старт системы запускается с режима тестирования оборудования (команды BIOS), а только потом управление передается загружаемой операционной системе.

Как проверить, работает ли процессор?

Теперь посмотрим на некоторые аспекты проверки работоспособности процессора. Нужно четко понимать, что, если бы процессор не работал, компьютер бы не смог начать загрузку вообще.

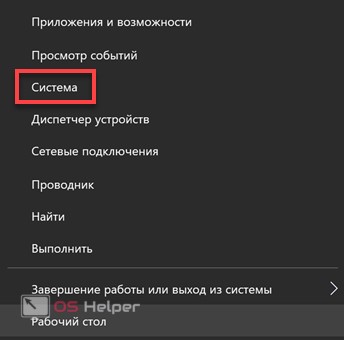

Другое дело, когда требуется посмотреть на показатель использования возможностей процессора в определенный момент. Сделать это можно из стандартного «Диспетчера задач» (напротив любого процесса указано, сколько процентов загрузки процессора он дает). Для визуального определения этого параметра можно воспользоваться вкладкой производительности, где отслеживание изменений происходит в режиме реального времени. Расширенные параметры можно увидеть при помощи специальных программ, например, CPU-Z.

Кроме того, можно задействовать несколько ядер процессора, используя для этого (msconfig) и дополнительные параметры загрузки.

Возможные проблемы

Наконец, несколько слов о проблемах. Вот многие пользователи часто спрашивают, мол, почему процессор работает, а монитор не включается? К центральному процессору эта ситуация не имеет никакого отношения. Дело в том, что при включении любого компьютера сначала тестируется графический адаптер, а только потом все остальное. Возможно, проблема состоит как раз в процессоре графического чипа (все современные видеоускорители имеют собственные графически процессоры).

Но на примере функционирования человеческого организма нужно понимать, что в случае остановки сердца умирает весь организм. Так и с компьютерами. Не работает процессор - «умирает» вся компьютерная система.

Расклад сил

Год назад мы уже рассказывали о новом в кратком обзоре « ». (Кстати, применять аббревиатуру APU мы тут не будем, используя более знакомый термин .) Рассматривать Llano отдельно от остальных двух новинок этого года от AMD было бы неверно, ибо компания весьма точно разделила потребителей на сегменты, покрыв новыми процессорами почти всё, что до 2011 г. было отдано на откуп Феномам, Атлонам и Семпронам. Главной идеей создания гибридных ЦП было помещение графического процессора (ГП) на кристалл центрального, названное маркетологами «слиянием» (Fusion). Ранее интегрированная графика у AMD существовала лишь в северном мосте чипсета (у Intel её в 2010 г. переместили в ЦП, но оставили отдельным , причём изготовленным по худшей ). А какая вообще графика требуется пользователям?

- Простая: для интернета, офиса, фильмов и старых игр - только это до сих пор и могла обеспечить «интеграшка»;

- Быстрая: в т. ч. для современных игр - такой уровень и сейчас под силу только отдельным видеокартам, цена которых чаще всего больше, чем у ЦП;

- Средняя: в т. ч. для игр, но либо не самых современных, либо не с самыми крутыми настройками, а главное - в компактном и тихом корпусе и за весьма ограниченный бюджет.

Именно для таких среднячков и сделан Llano. Он точно не поставит рекорды ни в одной категории, которой обычно сравнивают процессоры - ни по скорости (причём и в графической, и в вычислительной частях), ни по экономии, ни по цене. Его цель - занять золотую середину между всеми крайностями. Хотя нельзя сказать, что новизны нет совсем: гибридный ЦП впервые позволил сделать систему одновременно компактную (даже северный мост не нужен), пригодную для большинства игр и доступную почти всем игрокам. Например, всё более популярный форм-фактор «всё-в-одном» (монитор и системный блок в одном корпусе) теперь получит достойную 3D-графику.

Помимо того, что хотят массы, AMD должна была учесть и собственные возможности, которые сильно рассеяны из-за внедрения в течение года трёх , причём каждая - по новому для фирмы (совершенно немыслимая для конкурента ситуация - с их известной стратегией «тик-так»). Поэтому в данном случае (из трёх) ради минимизации рисков и экономии денег и времени решили не делать новую -архитектуру, а в очередной (но последний) раз обновить и дополнить старую. Так получились K12, пришедшие на смену K10.

Впрочем, весь процессор мог «получиться» куда раньше. Дело в том, что впервые идея об APU была заявлена из уст представителей AMD ещё в 2006 г., почти одновременно с покупкой ATI. Уже через год планов было громадье: сначала готовилась интеграция двух кристаллов в корпусе (как сделала Intel), затем - на одном кристалле, но со слабым взаимодействием (видимо, с отдельным КП для графической памяти), потом - с разделяемыми ресурсами, и, наконец, с полным «сплавом» вычислительных блоков общего и графического назначений. Причём шаг №1 должен был произойти уже в 2008 или 2009 г. Ясно, что многое пошло не так, а сложная финансовая ситуация заставила AMD даже выделить производственные мощности в виде отдельной компании Global Foundries (GF). Потерянное время пришлось навёрстывать авралом, так что первый вышедший APU оказался сразу третьим шагом вышеозначенного плана.

Если кратко перечислить суть Llano, то получится вот что:

- 2–4 ядра K12, суть - улучшенные K10;

- по 0,5 или 1 МБ на ядро, без ;

- накристальный ГП класса HD 5000;

- более скоростной , чем у K10, но лишённый за ненадобностью поддержки ;

- контроллер шины PCIe 2.0, в т. ч. для подключения внешней видеокарты или двух;

- более агрессивный авторазгон 2.0 (TC), но только для x86-ядер;

- шин питания x86-ядер, ГП и блока UVD;

- кристалл изготовлен по 32 нм технорме.

Интересно, что AMD ради высокой производительности GPGPU и некоторых других вычислений (в т. ч. перекодировании видео) сделала оптимизацию случая, когда графические и x86-ядра работают над общими данными - при этом их не требуется копировать из общей (когерентной) памяти в графическую и обратно. Интерфейс OpenCL даёт сразу несколько способов это сделать. Например, область памяти типа USWC (некэшируемая, упреждающая, со слиянием записей) обычно используется под кадровый буфер, но графические и x86-ядра могут получать к ней доступ поочерёдно. Также можно объявить некоторые страницы «фиксированными» (pinned), которых накладываются на непрерывно (для облегчения трансляции) - тогда любые ядра могут одновременно получать в них доступ, хотя для ГП так будет медленней.

Впрочем, эта оптимизация меркнет при рассмотрении пропусков разных видов обменов. На схемах видно, что максимум ПСП для одно- и многопоточного обменов между памятью и x86-ядрами - всего 8 и 13 ГБ/с, т. е. 27% и 43% от теоретического пика. Цифры для ГП - 40% и 57%. Тут, правда, не ясно, допустимо ли сложение чтений и записей - если да, то ситуация несколько лучше: одновременно читая и записывая, только x86-ядра могут в многопотоке загрузить 87% ПСП, а только графические - 97%. Тем не менее, странно, почему для каждого случая мы не можем получить 100%. Возможно, дело как раз в том самом приоритете для ГП, который понижает ПСП и для себя (когда простаивают x86-часть), и для x86 (когда молчит уже ГП).

Ещё меньше пропуски при обменах с чужими адресными пространствами, но тут объяснения есть: где-то нет кэширования в L2, а только буферы (WC, по 4 на ядро); где-то нужны снуп-проверка и трансляция адресов. В любом случае, AMD ещё надо хорошо поработать, чтобы нагрузить на полную широкие внутренние шины и внешнюю память. Для сравнения, ещё более широкая кольцевая шина в Sandy Bridge сразу даёт весь свой теоретический максимум, т. к. подключена к кэшу L3. Наконец-то 32!

Тут GF явно в догоняющих. Её 32-нанометровый техпроцесс на частично обеднённых КНИ-пластинах (PD-SOI) использует HKMG-транзисторы с напряжённым кремнием, изготовленные по методу «затвор первым» (детали обо всех этих технологий см. в нашем ). По утверждению GF, на кристалле могут присутствовать транзисторы, настроенные под три разных напряжения срабатывания - от 0,8 до 1,3 В (какие из них фактически используются в Llano - не ясно). Поверх них - 11-слойная медная металлизация с низкопроницаемыми диэлектриками; шаг затвора с учётом его контакта до одного из нижних трёх слоёв дорожек - 104 нм (для сравнения параметры Intel: 9 металлов и 112,5 нм - детально значение этих цифр исследовано в наших ). Есть несколько разных видов ячеек СОЗУ с разным сочетанием площади, потребления и скорости. Также допустимы (TSV), хотя на практике их в AMD пока никто не показал. В общем, всё примерно как у Intel, но в массовом производстве - на год позже.

Из тонких особенностей выделяются специальные транзисторы, корректирующие фронты сигналов для борьбы с утечками и выравнивания параметров всего массива транзисторов на многобитных шинах. Причём такая мера является «костылём», вызванным тем, что без него переведённое с 45 на 32 нм ядро заработало бы не так хорошо. При этом присутствуют и некоторые штатные средства экономии, в полном наборе имеющиеся в ядрах Bulldozer, изначально сделанных под 32 нм - детально поговорим о них в грядущей статье об этой архитектуре.

Разумеется, никак не обойти замену 6-транзисторных ячеек СОЗУ в кэшах на 8-транзисторные; зачем это надо - описано . (Кстати, впервые Intel применила такой приём экономии в Pentium 4 при переходе на 65 нм - разумеется, не для того, чтобы сделать его ультрамобильным, а т. к. иначе даже на новом техпроцессе не укладывались в предел по .) Но тут есть любопытный момент: замена почему-то почти не отразилась на площади кэшей. Чтобы разобраться с хитростями 32 нанометров у AMD, самое время заняться любимым делом процессорных аналитиков - подсчётом транзисторов:)

Кристалл 4-ядерного Llano

Итак, 4-ядерный Llano (с текущими и частотами потребляющий 35–100 Вт) имеет площадь 228 мм², на которых расположились 1450 млн. транзисторов (как обычно, сократим эту меру до «Мтр»). При этом на рекламном слайде AMD утверждает, что на x86-ядра и ГП ушло по 35%, а на СМ - 30%. Звучит крайне сомнительно: по расчётам, внеядро K10 (за вычетом контроллера и драйвера(ов) шины ) занимает ≈16 Мтр, а присутствующие тут блок UVD и контроллер PCIe никак не тянут на 419 Мтр. Возможно, речь шла о соотношении потраченной площади, что близко к реальности, но совсем не показательно, поэтому вернёмся к транзисторам. 2-ядерная версия кристалла (неизвестной пока площади) получит 758 Мтр и ГП на 240 «ядер».

Каждое ядро x86 занимает 9,69 мм² без учёта L2 и 17,7 мм² с L2. Транзисторов в нём «более 35» Мтр (у K10 было 30) + 1,38 на силовые ключи, а вместе с L2 - 110 Мтр. Предположим, что «более 35» означает «меньше 35,5», и получим ≈73,5 Мтр на мегабайт L2. Вычисленное значение для K10 - 76,25. Разница небольшая, но меньше это число точно стать не должно. Выходит, что либо ранее мы недооценивали сложность ядра K10 (где должно быть примерно на 3 Мтр больше), либо AMD (как уже многажды бывало) снова «намудрила» с цифрами. Проверим выкладки так: в «лишние» 5 Мтр должны уложится по 2 тр./бит в 128 КБ обоих L1 (это 2,1 Мтр), дополнительные 512 72-битных (скорее всего, тоже 8-транзисторных) ячеек для L2D TLB (+ 0,3 Мтр), а почти всё остальное - добавленная логика (в частности, целочисленный делитель - штука весьма немалая). Вроде всё совпадает. Видимо, «110» были округлены вниз примерно на 3 Мтр. Тем не менее, примем данное число.

Подсчитаем транзисторный бюджет большого и малого ГП + UVD + СМ: 1450−4×110=1010 и 758−2×110=538 Мтр. А теперь заглянем в той же архитектуры (изготавливаются на 40-нанометровом техпроцессе компании TSMC) и обнаружим вышеупомянутый Redwood с такими же параметрами, что и у старшего ГП Llano, но с транзисторным бюджетом лишь в 627 Мтр (включая контроллеры двух шин). А в наши 1010 Мтр уместится почти целый Juniper, который вдвое круче по всем параметрам! Далее, можно вычесть цифры Juniper из Redwood, т. к. эти ГП прежде всего отличаются формулой графических ядер и спаренных с ними спецблоков. Получаем 413 Мтр на 400 ФУ, 20 TMU и 8 ROP. Если же аналогично вычесть старший ГП Llano из младшего, то получится 472 Мтр на 160 ФУ, 8 TMU и 4 ROP!

Корпус (с варварски содранной крышкой) и основной кристалл XCGPU

Можно зайти с другой стороны - год назад был представлен чип, имеющий полное право называться первым массовым APU - XCGPU, процессор для нового поколения приставки Xbox моделей S. Предыдущие версии имели ЦП и ГП отдельно, тут же 45-нанометровое изделие GF умещает:

- 3 ядра ЦП (чуть модифицированные версии миниядер PPE из ЦП IBM Cell), работающие на частоте 3,2 ГГц;

- 1 МБ общего для них кэша L2, работающего с половинной частотой и подключенного к 256-битной шине;

- 500 МГц ГП AMD Xenos на 240 ФУ с пиковой производительностью в 240 Гфлопс;

- на втором чипе, связанном 500-мегагерцовой 512-битной шиной - 8 ROP и кадровый буфер на 10 МБ с архитектурой eDRAM (встроенное динамическое ОЗУ с 1-транзисторными ячейками).

Один корпус вместо двух (у прошлого ГП кадровый буфер также сидел рядом вторым кристаллом) сэкономил 60% TDP и 50% площади. На 10 МБ ОЗУ + ROP ушло 105 Мтр, т. е. для 8 ROP остаётся всего ≈10 Мтр. Но главное для нас то, что у основного чипа - 372 Мтр, из которых 165 ушло на ЦП + L2, а 232 - на ГП. И вот эта последняя цифра совсем не вяжется с похожим (в т. ч. по пиковой скорости) младшим ГП в Llano, которому, как мы подсчитали по не менее официальным цифрам, выпало 538 Мтр. В общем, веселуха с транзисторами продолжается - видимо, на техасщине это тоже популярная забава:) Кристалл со странностями

Теперь вернёмся к x86-ядрам. Тут полезно сделать небольшую ретроспективу. Давным-давно жила-была компания DEC - один из мировых лидеров по производству мэйнфреймов, миникомпьютеров и рабочих станций. И была в ней группа талантливых разработчиков микроархитектур, из-под руки которых вышли всемирно известные PDP-11, VAX и Alpha. О последней стоит сказать особо: её первая версия, Alpha 21064 или EV4 (1992 г.), это первый -процессор, частота которого превысила самые быстрые доселе компьютеры на ЭСЛ-логике. Второе поколение (21164 или EV5 - 1995 г.) - первый ЦП со встроенным L2 (который, правда, убрали из ЦП следующей версии). 21264 (EV6, 1998 г.) - второй (после AMD K5) 4-путный ЦП с (и с рекордными для логики 15,2 Мтр). 21364 (EV7, 2003 г.) - первый ЦП с высокоскоростным ИКП и сетевой межпроцессорной шиной. Планировавшийся на 2004 г. 21464 (EV8) должен был стать первым на 8 IPC и с 4-путной .

Но из-за просчётов руководства (и неожиданного для всех скачка производительности у x86 с выходом Pentium Pro) компьютеры с ЦП Alpha становились всё менее популярны, DEC терпела убытки, пока не была куплена компанией Compaq в 1998 г. Последняя свои микросхемы не разрабатывала и не производила (являясь активным покупателем ЦП Intel), так что судьба инженеров, продолжавших дорабатывать Альфы, была весьма печальна. В 2001 г. все наработки по Alpha (включая исследования по SMT, которые позже вырастут в технологию HyperThreading) Compaq продала в Intel, а та пригласила технарей работать над будущим Itanium (совместно с HP). (Говорят, большинство из перешедших 300 с чем-то инженеров до сих пор работают над новыми версиями этих ЦП.) Но часть персонала ушла ещё при кончине DEC…

…И ушла в AMD! Более того, Дэррик «Дёрк» Мэер, один из создателей Альфы, перешёл в AMD ещё в 1996 г. Возглавив группу, во многом состоящую из своих бывших коллег, он стал работать над новым ЦП. И уже в 1999 г. вышел первый Athlon. ЦП, разумеется, сделан с нуля, но в нём использовалась системная шина с технологией , первоначально разработанная для Alpha 21264. А в первых Opteron применили ИКП и шину HyperTransport, также от наработок для Alpha. Атлоны позволили в первый (и, пока, в последний) раз на равных соревноваться с Intel, пока та соображала, что бы такого сделать с Pentium 4… В общем, без команды архитектурщиков и инженеров из DEC об AMD сейчас бы вспоминали не чаще, чем о VIA. Но самое интересное для нас тут - как выглядели ядра Атлонов с первого по последний, и, для сравнения, Llano (по ссылкам - крупные версии):

| K7, 250 нм, 1999 г. | K7, 180 нм, 2001 г. | K8, 130 и 90 нм, 2003 и 2004 гг. |

|

||

| K8, 65 нм, 2006 г. | K10, 65 и 45 нм, 2007 и 2009 гг. | K12, 32 нм, 2011 г. |

Ясно, что любое сделанное с нуля ядро будет иметь совершенно новую раскладку блоков, с учётом архитектуры, техпроцесса и прочих параметров. Однако лицо Атлонов словно застряло во времени: за 12 лет на семи поколениях техпроцессов взаимное расположение и даже относительный размер основных блоков почти не изменились! Для сравнения, за это время Intel сделала с нуля P4, P-M, Core 2, Nehalem и Atom (не считая тех же Itanium и других не x86-ЦП), каждый их которых имеет совершенно отличный расклад ядра. Нельзя сказать, что в AMD сидят лентяи - просто либо первоначальный расклад оказался исключительно удачным, либо (что куда более вероятно) в AMD не хватило людских ресурсов, чтобы разработать совершенно новую микроархитектуру ранее 2011 г. Поэтому каждый раз ограничивались такими обновлениями существующей, чтобы они не повлекли полной переделки ядра.

Впрочем, кое-какие сдвиги в K12 всё же достойны комментария. Из-за удлинившегося целочисленного (включающего в себя и резервации) контроллер L2 «вылез» дальше остальных блоков, так что по обе стороны от него есть полосы свободного места. Особенно его много у L1I - настолько, что, немного потеснившись в логике фронта, его можно было бы увеличить на 50%. В других местах тоже стало посвободней - прежде всего из-за чуть более широких кэшей. Однако не смотря на их перевод с 6- на 8-транзисторную ячейку, относительная длина у них почти та же, что и у K10. Тем не менее, инженеры могли бы сократить несколько долей миллиметра по длине, пересобрав некоторую мешающую этому логику. Но не сделали это либо из-за недостатка времени, либо за ненадобностью.

Ладно там независимые аналитики из интернетов - но как AMD умудрилась ошибиться в разрисовке своего же кристалла, проведя границу блока UVD по его середине?..

А причина ненадобности может оказаться весьма проста - по ширине 4-ядерный кристалл ограничен длиной ГП. В результате парам x86-ядер не тесно даже с мегабайтовыми кэшами L2 - вокруг них полно свободного места. А ведь можно было ограничиться половиной L2 и развернуть ядра и СМ на 90° - сверху от них (по фото) освободится пространство, где можно разместить половину драйверов шин памяти, а вторую - вдоль левого края (ничего страшного, у Athlon II X2 эта полоска имеет аж два излома). В результате чип станет чуть длиннее (на ширину драйверов ОЗУ), но куда у́же.

Рассмотрим теперь ГП. Сразу можно сделать наблюдение: каждый большой прямоугольный блок устроен по принципу «массивы - по периметру, логика - по центру». Массивы - это мелкие горизонтальные прямоугольнички, устройство которых удивительно похоже по всему ГП. Зато логика, наоборот, совершенно хаотична. Такая комбинация может быть, только если и логику, и массивы оптимизировали по площади (и, во вторую очередь, экономии) в ущерб частоте. Но тут она и не нужна - выше 850 МГц не поднимаются даже дискретные ГП этой архитектуры. Тем не менее, линейная регулярность в логике должна быть, но тут она видна только на крупноблочном уровне: можно сказать точно, что 5 столбцов одинаковых блоков по 5 строк - это те самые 400 ФУ и 20 TMU. Число ROP (8) не делится на 5, и т. к. вряд ли одна пара рендер-блоков отключена даже в старшем ГП - их среди регулярных столбцов, видимо, нет…

Одна из пяти строчек с (предположительно) 80 графическими ФУ в ГП Llano

Резонно предположить, что вычислительные тракты займут наибольшую часть места, и это будут два похожих столбца по центру. Однако неясно, почему они хоть немного, но отличаются, и почему в каждом из них должно быть по 8 пятёрок 32-битных ФУ, но визуально ничего подобного не наблюдается… Выходит, либо AMD играет с Фотошопом (как это до сих пор продолжается с изображениями кристалла 4-модульного Bulldozer - скоро увидите), либо инженеры бывшей ATI намудрили что-то такое, что распознать это не могут даже видавшие всякого аналитики:)

Впрочем, кое-что всё же видно: по периметру каждой половины блока есть 64 одинаковых регулярных массива. При этом в вычислительную часть SIMD-блока (помимо 80 SP) входят 16 (РФ) по 1024 128-битных регистра. Плотность этих РФ в битах/мм² оказывается лишь чуть меньше плотности кэша L2 для x86-ядер и примерно в 20 раз лучше, чем у векторно-вещественного РФ там же. И это при обязательной многопортовости! Вот какие транзисторные оптимизации доступны при низких целевых частотах.

Теперь сообразим, как выглядит 2-ядерный кристалл с младшим ГП на 240 ФУ и половиной ROP. Все уже заметили «трещину» посреди ГП? Очевидно, это и есть «линия разреза», остаться после которого суждено только нижней части - вместе с нижней парой x86-ядер. Но постойте, ведь в верхней половине ГП есть ещё куча нужной логики и блок UVD - где будут они? Допустим, что их уместят встык к ФУ и TMU, но тогда придётся подвинутся драйверам ОЗУ, которые должны быть расположены либо углом, либо в 4 ряда (а не в 2, как сейчас: по числу каналов).

Не меньший вопрос - насчёт «потерянных» двух ROP. По 4 этих блока должны оказаться по разные стороны «трещины» (у всех старших ГП их 8, а у младших - 4). Но не считая вышеуказанных пяти «вычислительных столбцов», все остальные блоки и сверху и снизу разные. Если кто-то из читателей сможет аргументированно привязать хоть что-то из них к схеме ГП - добро пожаловать в комментарии на форуме. Стоит добавить, что при сравнении с не менее качественным фото ядра APU Zacate (с ГП на 80 ФУ той же архитектуры) ничего похожего на структуры из Llano не видно… Экономия

Первый пункт - цифровое предсказание потребления в модуле управления питанием (Digital APM). До сих пор APM работал примерно так: собирая аналоговые данные с термодиодов и датчиков тока, модуль их оцифровывал и делал выводы об общем потреблении. Цифровой APM таким методом только подтверждает ранее сделанное предсказание, основанное на сборе статистики по загрузке отдельных блоков. Зная её и зависимость потребления этого конкретного блока от его прошлой и текущей нагрузок, можно вычислить, сколько через мгновение должен потреблять весь чип, исходя из его математической модели. Смысл этого в том, что предсказание делается куда быстрее реальных измерений, причём его не надо предварительно калибровать под особенности конкретного кристалла, как того требуют аналоговые датчики. Цифровой APM, замеряя 95 сигналов и ошибаясь менее чем на 2%, обеспечивает более быстрые подстройки частот и напряжений при колебаниях нагрузки - ещё до того, как кристалл среагирует изменением температуры.

Любопытная хитрость, позволяющая цифровой модели там мало отклоняться от реальности, заключается в том, что APM учитывает теплопроводность отдельных участков кристалла, зная их расположение, площадь и локальную температуру. Поток тепла перераспределяется из работающих блоков в соседние, которые, возможно, простаивают, оттягивая на себя часть тепла. Учитывая, что тепло отводится через всю поверхность чипа, но имеет ограничение по потоку (≈50 Вт/см²) - чем с большей площади идёт охлаждение, тем лучше. Таким образом, горячее место на кристалле, если оно окружено простаивающими блоками, будет охлаждаться не только над собой, но и немножко сбоку, что и учитывает модель APM. Ей надо также учесть, что технология кремния-на-изоляторе (), при всех её технических преимуществах, имеет и недостаток: слой диоксида кремния работает в качестве не только электро-, но и термоизолятора. При прочих равных КНИ-кристалл имеет больше шансов перегреться. Но AMD с этим знакома уже давно и наверняка что-то придумала:)

Пилообразная граница между доменами питания у Llano удлиняет периметр, позволяя разместить над двойным набором ключей (вертикальные пунктиры) силовые контакты (квадраты) смежных доменов для экономии места под ключи. Иллюстрация с доклада для конференции ISSCC

Второй момент - силовые ключи , подключающие «землю» к ядрам (шины питания тут всегда включены). Используются n-канальные транзисторы, эффективность которых в качестве ключей (особо низкое сопротивление во включенном режиме и особо высокое в выключенном) оказывается лучше, чем у p-канальных - что является следствием применения КНИ. Intel использует p-канальную коммутацию шин питания - т. к. у неё техпроцесс на цельном кремнии. AMD утверждает, что n-канальные транзисторы меньше и быстрее при тех же электрических параметрах. В результате утечка тока у отключенного ядра уменьшена в 10 раз. Фактические тесты действительно подтверждают резкое сокращение потребления ЦП при частичной или нулевой загрузке.

Карта утечек тока Llano (красный - больше, синий - меньше) при нулевом тактировании, полученная с помощью «meridian photon recombination». При этом никакого другого упоминания этой фразы в сети больше нет - что же это за загадочный метод? И почему часть ГП странно замазана?..

AMD также показала карту утечек тока в трёх случаях: когда цепи включены, когда выключен блок UVD и когда выключена вся графика. x86-ядра, разумеется, могут отключаться по отдельности в C6. При усыплении всех ядер напряжение на шине их питания снижается, чтобы уменьшить даже эту мизерную утечку. При этом APM позволяет усыпить ядро как по его просьбе (т. е. от исполняющейся на нём программе), так и по команде ОС (которая исполняется в другом ядре). Усыпление ГП происходит после неактивности в течение заданного времени. Усыпление UVD и контроллера PCIe - программное, через драйверы и BIOS соответственно.

| Засыпание ↓ | Пробуждение |

| Ядро активно | |

| Смыв кэшей | |

| Сохранение состояния в ОЗУ | |

| Инициализация кэшей | |

| Запуск загрузочного микрокода (как после сброса) |

|

| Подключение перемычек с коррекцией микрокода |

|

| Понижение частоты | Повышение частоты |

| Отключение PLL | |

| Отключение шин до СМ | Подключение шин до СМ |

| Отключение силовой шины | Подключение силовой шины |

| Включение и калибровка PLL | |

| Ядро спит | |

В этой таблице указаны процедуры засыпания в состояние C6 и пробуждения из него. Последнее занимает 30 мкс для одного ядра и 100 мкс для всего ЦП (включая пробуждение модулей памяти), причём AMD обещает даже эти достойные цифры ещё улучшить. (Можете их сравнить с моделей Z6xx.) При этом в спящем ЦП всё равно работает APIC - программируемый контроллер прерываний, реагирующий на внешние события, включая регулярные пробуждения по таймеру. В отличие от того же «Атома», AMD не стала внедрять специальное буферное для хранения состояния ядра на кристалле, разумно полагая, что пока будут выполняться остальные процедуры, ИКП успеет подкачать нужные несколько сот байт.

Заметим, что шин питания , у Llano - две: для x86-ядер и всего остального, включая ГП (кроме умножителей, для которых есть отдельная слаботочная шина). Это чуть удешевляет плату, но не приводит к неоптимальному потреблению энергии. Второе напряжение является максимумом из потребностей СМ (включая ИКП), ГП, UVD и контроллера PCIe. При декодировании видео ГП простаивает, но запитывается полными вольтами - однако они не доходят до потребления, остановленные силовыми ключами. Похоже, что AMD нашла оптимум между ценой и экономией.

Наконец, третья добавка - разряжённая сеть тактирования . Через неё умножитель частоты передаёт потребителям тактовые импульсы нужной им частоты. Требуется, чтобы все импульсы дошли строго одновременно до всех частей потребителей, что вынуждает строить разветвлённое дерево дорожек, высчитывая их длину так, чтобы задержка распространения сигнала до любой конечной ветки была одинакова. Учитывая затухание сигнала, приходится регулярно ставить усилители, вносящие собственную задержку. В результате на полной частоте вся эта сеть потребляет значительную энергию, даже если никакой полезной работы не выполняется. Например, у Pentium 4 на её питание уходило до трети потребляемой мощности.

В AMD поступили так же, как и создатели Atom: сократили число буферов и усилителей вдвое, а число ветвей - впятеро, удалив ненужные с учётом нагрузки. Теперь при полной выкладке Llano тактирует всего 32% блоков (только фактически работающие), а при простое (без отключения блоков) - лишь 12%. Так получилось уменьшить на 54% потребляемую сетью мощность. Опять же - всё со слов AMD. В таблице рядом показаны результаты моделирования максимального потребления при питании 1 В.

Ещё три технологии касаются конкретно ГП. Во-первых, адаптивная модуляция подсветки (adaptive backlight modulation, ABM) плавно затемняет лампы или светодиоды подсветки при выводе «тёмной» картинки - при этом выводимые пиксели пропорционально осветляются, чтобы воспринимаемое изображение имело верную яркость. Во-вторых, сжатие кадрового буфера позволяет выводить только изменённые части кадра относительно предыдущего - с сильной экономией трафика шины (много ли пикселей меняется от кадра к кадру при перемещении курсора?). В-третьих, внешний ГП при простое спит, потребляя всего 0,2 Вт (с готовностью проснуться за 0,15 с), хотя это больше заслуга его устройства, а не процессора.

Что всё это даст потребителю? А то, что впервые со времён мобильных Pentium 4 AMD предложила платформу, достаточно экономную, чтобы если не выиграть, то хотя бы на равных соревноваться с соперником (при одинаковой скорости и ёмкости батарей). При этом вариант AMD стоит дешевле, если систему на базе Intel оснастить дискретным ГП, сравнимым со встроенным в Llano. Turbo Core 2.0

Экономия ватт даст больше шансов разогнать работающие ядра, что будет посильнее призрачных «6%», когда вычислительная производительность нужна во что бы то ни стало. Поможет в этом новый (по сравнению с внедрённым в Phenom II X6) алгоритм Turbo Core 2.0. Он работает во всех мобильных моделях, разгоняя их на 400-900 МГц, но не во всех настольных, где разгон - всего на 300 МГц. Причём для конкретного ЦП разгон либо включен, либо нет - никакой регулировки типа «от 100 до 500 МГц» нет. Если сравнить это с возможностями Turbo Boost, то видно, что AMD есть к чему стремиться.

Как и с Turbo Boost 2.0, теперь можно ненадолго превысить предел TDP, если температура ещё не подошла к своему лимиту. В версии 1.0 ускорение делалось на базе активности половины ядер, а не каждого по отдельности. Т. е. формула ускорения (приращение множителей при простое от N−1 до 0 ядер) для 6-ядерного Фенома выглядела так: x-x-x-0-0-0. Однако у Llano авторазгон присутствует и у 3-ядерного A6-3500 (т. е. с нечётным числом ядер), из чего можно сделать осторожный вывод, что TC 2.0, видимо, наконец-то научился работать с поядерной дискретностью. Проверить это, как ни странно, весьма трудно, т. к. AMD до сих пор не даёт возможность считать реальную частоту ядер. Кроме того, как уже сказано, не может ускоряться ГП. Пока… Модели, чипсеты и платформы

Как обычно, дадим ссылки на описания и моделей в Википедии и прокомментируем увиденное. Во-первых, не доверяйте всему, что там пишут над таблицами;) Во-вторых, знакомые имена ушли в прошлое, оставив лишь буквы и цифры. С буквами после номера модели просто: M - мобильная модель на 35 Вт, MX - на 45, K - настольная со свободным множителем. А вот их комбинации с цифрами уже возвращают нас в привычный бардак. В таблице указаны общие характеристики первых выпущенных видов Llano.

| Ряд | Число ядер | Объём L2, МБ | ГП | Turbo Core | Память | TDP, Вт |

| E2 | 2 | 0,5×2 | 6370D | нет | DDR3-1600 | 65 |

| E2-M | 6380G | у всех | DDR3-1333 | 35 | ||

| A4 | 2 | 0,5×2 | 6410D | нет | DDR3-1600 | 65 |

| A4-M | 1×2 | 6480G | у всех | DDR3-1333 | 35 | |

| A4-MX | 45 | |||||

| A6 | 3/4 | 1×3/4 | 6530D | иногда | DDR3-1866 | 65/100 |

| A6-M | 4 | 1×4 | 6520G | у всех | DDR3-1333 | 35 |

| A6-MX | DDR3-1600 | 45 | ||||

| A8 | 4 | 1×4 | 6550D | иногда | DDR3-1866 | 65/100 |

| A8-M | 6620G | у всех | DDR3-1333 | 35 | ||

| A8-MX | DDR3-1600 | 45 |

Казалось бы, куда логично назвать все 4-ядерные модели - A8, а отличия в ГП оставить лишь в номерах. Не менее разумно оснастить все A4 полными кэшами L2, а все MX-версии - памятью на 1600 МГц (иначе не ясно, почему на +200 МГц базовой частоты x86-ядер модели A4-3310MX в сравнении с A4-3300M угрохали лишние 10 Вт). Из номеров моделей пока можно узнать, что первая цифра - 3, последняя - 0, а две средние - чем больше, тем лучше. При всём идиотизме такого описания - это всё, что можно сказать, чтобы не пускаться в исключения.

Занятно, что TС отсутствует у 100-ваттовых ЦП, хотя, казалось бы, у них-то точно потолок разгона высокий… Куда хуже то, что, несмотря на все ухищрения, меньше 65 Вт у настольных моделей нет. Разумеется, надо отдать должное неслабому ГП (даже у A4 и E2), но как минимум с маркетинговой точки зрения (по сравнению с модельным рядом Intel) смотрится плохо.

С тех пор уже объявлены новые модели, описание которых показывает, куда расширяется модельный ряд:

- Помимо A8-3870K, планируется ещё одна разблокированная модель - A6-3670K на 2,7 ГГц (также без авторазгона) и ГП 6530D на 443 МГц. Таким образом, даже скромный игрок сможет быть разгонщиком;

- Готовятся 4-ядерные Athlon II X4 моделей 631, 641 и 651 на 2,6, 2,8 и 3 ГГц, 100 Вт TDP, без TC и даже без ГП. К ним присоединятся и 2-ядерные Sempron X2 198 на 2,5 ГГц и Athlon II X2 221 на 2,8 (оба - с 0,5 МБ L2 и TDP на 65 Вт). Все они уже не APU - потому, видимо, их и назвали старыми именами. Возможно, эти модели придут, когда современные ЦП на 45 нм уже уйдут на покой, а новые ещё не появятся;

- Модель A4-3305M отличается от A4-3300M тем, что имеет половинные кэши L2 и самый слабый ГП, зато последний работает на частоте 593 МГц (быстрее любого другого мобильного Llano). Таким образом, внезапная пятёрка внесла очередное исключение: по большинству характеристик 3305M относится к линейке E2;

- Планируемые модели ноутбуков HP Pavilion в списке доступных ЦП имеют и другие модели Llano, которые вносят ещё больший бардак (например, больший номер может означать меньшую частоту, а буква M - 45 Вт TDP). Впрочем, эти номера запросто могут бесследно исчезнуть…

Настольные модели используют -корпус для разъёма Socket FM1 на 905 выводов, а мобильные - FS1 на 722. В будущем возможны мобильные модели в -корпусе для распайки на плате, хотя для них почему-то также указывается разъём - FP1. Интересно, что для этих ЦП TDP указан как 20 или 26 Вт для 2-ядерных и 30 Вт для 4-ядерных - нижняя граница вплотную подходит к чипам Zacate с ядрами Bobcat…

От чипсетов остались лишь южные мосты, потому что северный уже весь «сынтегрирован» - и это вдвойне хорошо, т. к. уже известно, что они смогут работать как минимум с некоторыми ЦП из второго поколения APU, выходящего в 2012 г. Официально чипсет называется Fusion Controller Hub («узел управления слиянием», смех в зале ), а неофициально - Hudson. Изготавливается по технорме 65 нм в корпусе FCBGA-605 размером 23×23 мм. FCH для Llano делятся на два класса - мобильные M с TDP 2,7–4,7 Вт и настольные D на 5 Вт.

- Все версии имеют: 6 портов SATA 3.0 (на 6 Гбит/с), RAID 0/1, 4 порта PCIe 2.0 x1 и 3 PCI, VGA (аналоговая часть), звук HD Audio, 14 портов USB 2.0, гигабитный Ethernet, контроллер карт SD (до 32 ГБ и 25 МБ/с), встроенный тактовый генератор и поддержка UEFI (новый «BIOS»);

- M2 (он же - A60M, предназначен для платформы Sabine): стандартная модель;

- M3 (A70M, для Sabine): как M2, но 4 порта USB обновлены до версии 3.0;

- D1 (A45, для Value Lynx): отсутствуют Ethernet, RAID, SD и VGA; все порты SATA - только версии 2.0; + 1 порт PCI;

- D2 (A55, для Lynx и Carina): как M2, но с поддержкой RAID 10 и FIS-based switching (возможность подключения к порту SATA до 15 устройств через хаб-разветвитель);

- D3 (A75, для Lynx и Carina): как D2, но 4 порта USB обновлены до версии 3.0.

Платформа Sabine - для «обычных» ноутбуков, Value Lynx - дешёвые домашние ПК, Lynx - «просто» домашние ПК, а Carina - офисные ПК. Чем отличаются последние два - неясно. Итого

В теории всё выглядит хорошо: AMD малыми усилиями сделала ЦП, некоторые характеристики которых можно с полным правом назвать передовыми и даже уникальными, что и обеспечит им продажи. Заменив старые Атлоны и добавив к ним графику за меньшие деньги и ватты, можно почувствовать, что прогресс есть даже у ЦП с 12-летней микроархитектурой. Но всему приходит конец - выходящее весной 2012 г. второе поколение APU Trinity уже будет использовать новые ядра Piledriver («улучшенный Бульдозер») и новый разъём Socket FM2 на 904 вывода (специально несовместимый с нынешним). В Trinity обещают ГП с новой архитектурой VLIW4 (используется пока только в чипе Cayman, он же Radeon HD 69x0), аппаратный видеокодер (VCE), подключение до трёх мониторов, наличие TC версии 3.0 (с разгоном ГП), поддержку DDR3-2133 и PCIe 3.0, 65–125 Вт TDP и обновлённые чипсеты.

А в следующих поколениях встроенных ГП на базе архитектуры «Southern Islands» появятся: лучшая поддержка языков высокого уровня для GPGPU (с использованием более привычной суперскалярных -ядер вместо ), общее адресное пространство с x86, 64-битная виртуальная адресация с подкачкой страниц, переключение контекста (для многозадачности) и протокол когерентности для PCIe (чтобы всё вышеперечисленное было возможно и для внешнего ГП).

На радостях от выпуска новых ЦП в AMD даже считать разучились, заявив в одном из слайдов, что «APU знаменуют самый большой сдвиг в технологии ПК с момента изобретения x86-ЦП более 40 лет назад». Изобретения? Более 40 лет назад? Ну, пока кто-то в AMD открывает для себя непознанные страницы истории (или арифметики) - отдадим дань окончательно уходящим на покой Атлонам. Из них выжали всё, и этого хватило надолго.